# 24. Peripheral DMA Controller (PDC)

## 24.1 Description

The Peripheral DMA Controller (PDC) transfers data between on-chip serial peripherals and the on- and/or off-chip memories. The link between the PDC and a serial peripheral is operated by the AHB to ABP bridge.

The PDC contains 22 channels. The full-duplex peripherals feature 21 mono directional channels used in pairs (transmit only or receive only). The half-duplex peripherals feature 1 bidirectional channels.

The user interface of each PDC channel is integrated into the user interface of the peripheral it serves. The user interface of mono directional channels (receive only or transmit only), contains two 32-bit memory pointers and two 16-bit counters, one set (pointer, counter) for current transfer and one set (pointer, counter) for next transfer. The bi-directional channel user interface contains four 32-bit memory pointers and four 16-bit counters. Each set (pointer, counter) is used by current transmit, next transmit, current receive and next receive.

Using the PDC removes processor overhead by reducing its intervention during the transfer. This significantly reduces the number of clock cycles required for a data transfer, which improves microcontroller performance.

To launch a transfer, the peripheral triggers its associated PDC channels by using transmit and receive signals. When the programmed data is transferred, an end of transfer interrupt is generated by the peripheral itself.

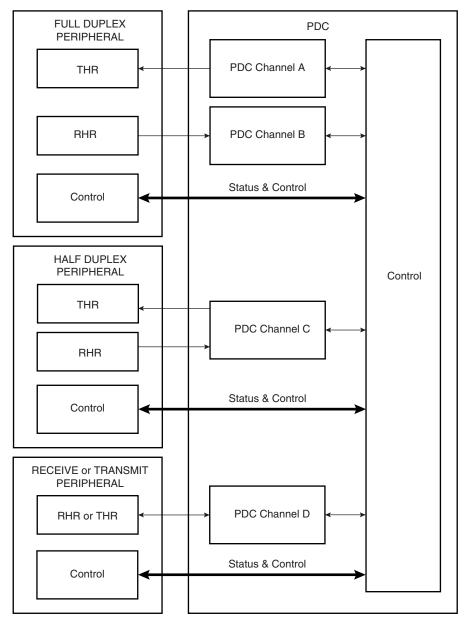

## 24.2 Block Diagram

Figure 24-1. Block Diagram

## 24.3 Functional Description

### 24.3.1 Configuration

The PDC channel user interface enables the user to configure and control data transfers for each channel. The user interface of each PDC channel is integrated into the associated peripheral user interface.

The user interface of a serial peripheral, whether it is full or half duplex, contains four 32-bit pointers (RPR, RNPR, TPR, TNPR) and four 16-bit counter registers (RCR, RNCR, TCR, TNCR). However, the transmit and receive parts of each type are programmed differently: the

transmit and receive parts of a full duplex peripheral can be programmed at the same time, whereas only one part (transmit or receive) of a half duplex peripheral can be programmed at a time.

32-bit pointers define the access location in memory for current and next transfer, whether it is for read (transmit) or write (receive). 16-bit counters define the size of current and next transfers. It is possible, at any moment, to read the number of transfers left for each channel.

The PDC has dedicated status registers which indicate if the transfer is enabled or disabled for each channel. The status for each channel is located in the associated peripheral status register. Transfers can be enabled and/or disabled by setting TXTEN/TXTDIS and RXTEN/RXTDIS in the peripheral's Transfer Control Register.

At the end of a transfer, the PDC channel sends status flags to its associated peripheral. These flags are visible in the peripheral status register (ENDRX, ENDTX, RXBUFF, and TXBUFE). Refer to Section 24.3.3 and to the associated peripheral user interface.

#### 24.3.2 Memory Pointers

Each full duplex peripheral is connected to the PDC by a receive channel and a transmit channel. Both channels have 32-bit memory pointers that point respectively to a receive area and to a transmit area in on- and/or off-chip memory.

Each half duplex peripheral is connected to the PDC by a bidirectional channel. This channel has two 32-bit memory pointers, one for current transfer and the other for next transfer. These pointers point to transmit or receive data depending on the operating mode of the peripheral.

Depending on the type of transfer (byte, half-word or word), the memory pointer is incremented respectively by 1, 2 or 4 bytes.

If a memory pointer address changes in the middle of a transfer, the PDC channel continues operating using the new address.

#### 24.3.3 Transfer Counters

Each channel has two 16-bit counters, one for current transfer and the other one for next transfer. These counters define the size of data to be transferred by the channel. The current transfer counter is decremented first as the data addressed by current memory pointer starts to be transferred. When the current transfer counter reaches zero, the channel checks its next transfer counter. If the value of next counter is zero, the channel stops transferring data and sets the appropriate flag. But if the next counter value is greater then zero, the values of the next pointer/next counter are copied into the current pointer/current counter and the channel resumes the transfer whereas next pointer/next counter get zero/zero as values. At the end of this transfer the PDC channel sets the appropriate flags in the Peripheral Status Register.

The following list gives an overview of how status register flags behave depending on the counters' values:

- ENDRX flag is set when the PERIPH\_RCR register reaches zero.

- RXBUFF flag is set when both PERIPH\_RCR and PERIPH\_RNCR reach zero.

- ENDTX flag is set when the PERIPH\_TCR register reaches zero.

- TXBUFE flag is set when both PERIPH\_TCR and PERIPH\_TNCR reach zero.

These status flags are described in the Peripheral Status Register.

#### 24.3.4 Data Transfers

The serial peripheral triggers its associated PDC channels' transfers using transmit enable (TXEN) and receive enable (RXEN) flags in the transfer control register integrated in the peripheral's user interface.

When the peripheral receives an external data, it sends a Receive Ready signal to its PDC receive channel which then requests access to the Matrix. When access is granted, the PDC receive channel starts reading the peripheral Receive Holding Register (RHR). The read data are stored in an internal buffer and then written to memory.

When the peripheral is about to send data, it sends a Transmit Ready to its PDC transmit channel which then requests access to the Matrix. When access is granted, the PDC transmit channel reads data from memory and puts them to Transmit Holding Register (THR) of its associated peripheral. The same peripheral sends data according to its mechanism.

#### 24.3.5 PDC Flags and Peripheral Status Register

Each peripheral connected to the PDC sends out receive ready and transmit ready flags and the PDC sends back flags to the peripheral. All these flags are only visible in the Peripheral Status Register.

Depending on the type of peripheral, half or full duplex, the flags belong to either one single channel or two different channels.

#### 24.3.5.1 Receive Transfer End

This flag is set when PERIPH\_RCR register reaches zero and the last data has been transferred to memory.

It is reset by writing a non zero value in PERIPH\_RCR or PERIPH\_RNCR.

#### 24.3.5.2 Transmit Transfer End

This flag is set when PERIPH\_TCR register reaches zero and the last data has been written into peripheral THR.

It is reset by writing a non zero value in PERIPH\_TCR or PERIPH\_TNCR.

#### 24.3.5.3 Receive Buffer Full

This flag is set when PERIPH\_RCR register reaches zero with PERIPH\_RNCR also set to zero and the last data has been transferred to memory.

It is reset by writing a non zero value in PERIPH\_TCR or PERIPH\_TNCR.

#### 24.3.5.4 Transmit Buffer Empty

This flag is set when PERIPH\_TCR register reaches zero with PERIPH\_TNCR also set to zero and the last data has been written into peripheral THR.

It is reset by writing a non zero value in PERIPH\_TCR or PERIPH\_TNCR.

## 24.4 Peripheral DMA Controller (PDC) User Interface

| Offset | Register                       | Name Access                |            | Reset |

|--------|--------------------------------|----------------------------|------------|-------|

| 0x100  | Receive Pointer Register       | PERIPH <sup>(1)</sup> _RPR | Read-write | 0     |

| 0x104  | Receive Counter Register       | PERIPH_RCR                 | Read-write | 0     |

| 0x108  | Transmit Pointer Register      | PERIPH_TPR                 | Read-write | 0     |

| 0x10C  | Transmit Counter Register      | PERIPH_TCR                 | Read-write | 0     |

| 0x110  | Receive Next Pointer Register  | PERIPH_RNPR                | Read-write | 0     |

| 0x114  | Receive Next Counter Register  | PERIPH_RNCR                | Read-write | 0     |

| 0x118  | Transmit Next Pointer Register | PERIPH_TNPR                | Read-write | 0     |

| 0x11C  | Transmit Next Counter Register | PERIPH_TNCR                | Read-write | 0     |

| 0x120  | Transfer Control Register      | PERIPH_PTCR                | Write-only | 0     |

| 0x124  | Transfer Status Register       | PERIPH_PTSR                | Read-only  | 0     |

### Table 24-1.Register Mapping

Note: 1. PERIPH: Ten registers are mapped in the peripheral memory space at the same offset. These can be defined by the user according to the function and the peripheral desired (DBGU, USART, SSC, SPI, MCI, etc.)

## 24.4.1 Receive Pointer Register

| Access Type: Read-write | Register Name: | PERIPH_RPR |    |     |     |    |    |    |  |  |

|-------------------------|----------------|------------|----|-----|-----|----|----|----|--|--|

| 31 30 29 28 27 26 25 24 | Access Type:   | Read-write |    |     |     |    |    |    |  |  |

|                         | 31             | 30         | 29 | 28  | 27  | 26 | 25 | 24 |  |  |

| RXPTR                   |                |            |    |     |     |    |    |    |  |  |

| 23 22 21 20 19 18 17 16 | 23             | 22         | 21 | 20  | 19  | 18 | 17 | 16 |  |  |

| RXPTR                   |                |            |    |     |     |    |    |    |  |  |

| 15 14 13 12 11 10 9 8   | 15             | 14         | 13 | 12  | 11  | 10 | 9  | 8  |  |  |

| RXPTR                   |                |            |    |     |     |    |    |    |  |  |

| 7 6 5 4 3 2 1 0         | 7              | 6          | 5  | 4   | 3   | 2  | 1  | 0  |  |  |

| RXPTR                   |                |            |    | RXI | PTR |    |    |    |  |  |

## • RXPTR: Receive Pointer Register

RXPTR must be set to receive buffer address.

When a half duplex peripheral is connected to the PDC, RXPTR = TXPTR.

# 24.4.2 Receive Counter Register

| Register Name | : PERIPH | I_RCR |    |     |    |    |    |  |  |

|---------------|----------|-------|----|-----|----|----|----|--|--|

| Access Type:  | Read-w   | rite  |    |     |    |    |    |  |  |

| 31            | 30       | 29    | 28 | 27  | 26 | 25 | 24 |  |  |

| -             | -        | -     | -  | -   | -  | -  | -  |  |  |

| 23            | 22       | 21    | 20 | 19  | 18 | 17 | 16 |  |  |

| -             | -        | -     | -  | -   | -  | -  | -  |  |  |

| 15            | 14       | 13    | 12 | 11  | 10 | 9  | 8  |  |  |

| RXCTR         |          |       |    |     |    |    |    |  |  |

| 7             | 6        | 5     | 4  | 3   | 2  | 1  | 0  |  |  |

|               |          |       | RX | CTR |    |    |    |  |  |

|               |          |       |    |     |    |    |    |  |  |

## RXCTR: Receive Counter Register

RXCTR must be set to receive buffer size.

When a half duplex peripheral is connected to the PDC, RXCTR = TXCTR.

0 = Stops peripheral data transfer to the receiver

1 - 65535 = Starts peripheral data transfer if corresponding channel is active

## 24.4.3 Transmit Pointer Register

| Access Type:   Read-write     31   30   29   28   27   26   25   24     TXPTR     23   22   21   20   19   18   17   16     TXPTR | Register Name: | PERIPH_TPR |            |     |     |    |    |    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------|------------|------------|-----|-----|----|----|----|--|--|--|

| TXPTR       23     22     21     20     19     18     17     16                                                                   | Access Type:   | Read-w     | Read-write |     |     |    |    |    |  |  |  |

| 23 22 21 20 19 18 17 16                                                                                                           | 31             | 30         | 29         | 28  | 27  | 26 | 25 | 24 |  |  |  |

|                                                                                                                                   | TXPTR          |            |            |     |     |    |    |    |  |  |  |

| TXPTR                                                                                                                             | 23             | 22         | 21         | 20  | 19  | 18 | 17 | 16 |  |  |  |

|                                                                                                                                   |                | TXPTR      |            |     |     |    |    |    |  |  |  |

| 15 14 13 12 11 10 9 8                                                                                                             | 15             | 14         | 13         | 12  | 11  | 10 | 9  | 8  |  |  |  |

| TXPTR                                                                                                                             |                |            |            |     |     |    |    |    |  |  |  |

| 7 6 5 4 3 2 1 0                                                                                                                   | 7              | 6          | 5          | 4   | 3   | 2  | 1  | 0  |  |  |  |

| TXPTR                                                                                                                             |                |            |            | TXI | PTR |    |    |    |  |  |  |

### • TXPTR: Transmit Counter Register

TXPTR must be set to transmit buffer address.

When a half duplex peripheral is connected to the PDC, RXPTR = TXPTR.

| 24.4.4   | Transmit | Counter Register |

|----------|----------|------------------|

| Register | Name:    | PERIPH_TCR       |

| Access Type:     Read-write       31     30     29     28     27     26     25       -     -     -     -     -     -     -     - |      |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|--|--|--|--|

| 31 30 29 28 27 26 25   - - - - - - -                                                                                             |      |  |  |  |  |  |  |  |  |

|                                                                                                                                  | 5 24 |  |  |  |  |  |  |  |  |

|                                                                                                                                  | -    |  |  |  |  |  |  |  |  |

| 23 22 21 20 19 18 17                                                                                                             | 16   |  |  |  |  |  |  |  |  |

|                                                                                                                                  | -    |  |  |  |  |  |  |  |  |

| 15 14 13 12 11 10 9                                                                                                              | 8    |  |  |  |  |  |  |  |  |

| TXCTR                                                                                                                            |      |  |  |  |  |  |  |  |  |

| 7 6 5 4 3 2 1                                                                                                                    | 0    |  |  |  |  |  |  |  |  |

| TXCTR                                                                                                                            |      |  |  |  |  |  |  |  |  |

### • TXCTR: Transmit Counter Register

TXCTR must be set to transmit buffer size.

When a half duplex peripheral is connected to the PDC, RXCTR = TXCTR.

0 = Stops peripheral data transfer to the transmitter

1- 65535 = Starts peripheral data transfer if corresponding channel is active

| 24.4.5 Receive<br>Register Name: | e Next Point<br>PERIPH | t <b>er Register</b><br>I_RNPR |     |      |    |    |    |  |  |

|----------------------------------|------------------------|--------------------------------|-----|------|----|----|----|--|--|

| Access Type:                     | Read-w                 | rite                           |     |      |    |    |    |  |  |

| 31                               | 30                     | 29                             | 28  | 27   | 26 | 25 | 24 |  |  |

| RXNPTR                           |                        |                                |     |      |    |    |    |  |  |

| 23                               | 22                     | 21                             | 20  | 19   | 18 | 17 | 16 |  |  |

| RXNPTR                           |                        |                                |     |      |    |    |    |  |  |

| 15                               | 14                     | 13                             | 12  | 11   | 10 | 9  | 8  |  |  |

| RXNPTR                           |                        |                                |     |      |    |    |    |  |  |

| 7                                | 6                      | 5                              | 4   | 3    | 2  | 1  | 0  |  |  |

|                                  |                        |                                | RXN | IPTR |    |    |    |  |  |

### • RXNPTR: Receive Next Pointer

RXNPTR contains next receive buffer address.

When a half duplex peripheral is connected to the PDC, RXNPTR = TXNPTR.

#### 24.4.6 Receive Next Counter Register Register Name: PERIPH BNCB

| Register Name | : PERIPH | I_RNCR     |     |      |    |    |    |  |  |

|---------------|----------|------------|-----|------|----|----|----|--|--|

| Access Type:  | Read-w   | Read-write |     |      |    |    |    |  |  |

| 31            | 30       | 29         | 28  | 27   | 26 | 25 | 24 |  |  |

| -             | _        | -          | -   | -    | -  | —  | -  |  |  |

| 23            | 22       | 21         | 20  | 19   | 18 | 17 | 16 |  |  |

| _             | _        | -          | —   | -    | -  | —  | -  |  |  |

| 15            | 14       | 13         | 12  | 11   | 10 | 9  | 8  |  |  |

| RXNCTR        |          |            |     |      |    |    |    |  |  |

| 7             | 6        | 5          | 4   | 3    | 2  | 1  | 0  |  |  |

|               |          |            | RXN | ICTR |    |    |    |  |  |

## • RXNCTR: Receive Next Counter

RXNCTR contains next receive buffer size.

When a half duplex peripheral is connected to the PDC, RXNCTR = TXNCTR.

| 24.4.7 Transm<br>Register Name: | it Next Poin<br>PERIPH | <b>ter Register</b><br>_TNPR |     |     |    |    |    |  |  |  |

|---------------------------------|------------------------|------------------------------|-----|-----|----|----|----|--|--|--|

| Access Type:                    | Read-wr                | ite                          |     |     |    |    |    |  |  |  |

| 31                              | 30                     | 29                           | 28  | 27  | 26 | 25 | 24 |  |  |  |

| TXNPTR                          |                        |                              |     |     |    |    |    |  |  |  |

| 23                              | 22                     | 21                           | 20  | 19  | 18 | 17 | 16 |  |  |  |

| TXNPTR                          |                        |                              |     |     |    |    |    |  |  |  |

| 15                              | 14                     | 13                           | 12  | 11  | 10 | 9  | 8  |  |  |  |

| TXNPTR                          |                        |                              |     |     |    |    |    |  |  |  |

| 7                               | 6                      | 5                            | 4   | 3   | 2  | 1  | 0  |  |  |  |

|                                 |                        |                              | TXN | PTR |    |    |    |  |  |  |

### • TXNPTR: Transmit Next Pointer

TXNPTR contains next transmit buffer address.

When a half duplex peripheral is connected to the PDC, RXNPTR = TXNPTR.

#### 24.4.8 Transmit Next Counter Register Begister Name: PERIPH TNCR

| Register Name | e: PERIPH | I_TNCR     |     |     |    |    |    |  |  |

|---------------|-----------|------------|-----|-----|----|----|----|--|--|

| Access Type:  | Read-w    | Read-write |     |     |    |    |    |  |  |

| 31            | 30        | 29         | 28  | 27  | 26 | 25 | 24 |  |  |

| -             | _         | -          | -   | -   | -  | —  | -  |  |  |

| 23            | 22        | 21         | 20  | 19  | 18 | 17 | 16 |  |  |

| -             | —         | -          | -   | —   | -  | —  | -  |  |  |

| 15            | 14        | 13         | 12  | 11  | 10 | 9  | 8  |  |  |

| TXNCTR        |           |            |     |     |    |    |    |  |  |

| 7             | 6         | 5          | 4   | 3   | 2  | 1  | 0  |  |  |

|               |           |            | TXN | CTR |    |    |    |  |  |

## • TXNCTR: Transmit Counter Next

TXNCTR contains next transmit buffer size.

When a half duplex peripheral is connected to the PDC, RXNCTR = TXNCTR.

## 24.4.9 Transfer Control Register

| Register Name | PERIPH   | I_PTCR |    |    |    |        |       |

|---------------|----------|--------|----|----|----|--------|-------|

| Access Type:  | Write-or | nly    |    |    |    |        |       |

| 31            | 30       | 29     | 28 | 27 | 26 | 25     | 24    |

| -             | _        | -      | -  | -  | -  | -      | -     |

| 23            | 22       | 21     | 20 | 19 | 18 | 17     | 16    |

| -             | -        | —      | -  | -  | -  | -      | -     |

| 15            | 14       | 13     | 12 | 11 | 10 | 9      | 8     |

| -             | —        | -      | -  | -  | —  | TXTDIS | TXTEN |

| 7             | 6        | 5      | 4  | 3  | 2  | 1      | 0     |

| -             | _        | -      | -  | -  | -  | RXTDIS | RXTEN |

|               |          |        |    |    |    |        |       |

### • RXTEN: Receiver Transfer Enable

0 = No effect.

1 = Enables PDC receiver channel requests if RXTDIS is not set.

When a half duplex peripheral is connected to the PDC, enabling the receiver channel requests automatically disables the transmitter channel requests. It is forbidden to set both TXTEN and RXTEN for a half duplex peripheral.

### • RXTDIS: Receiver Transfer Disable

0 = No effect.

1 = Disables the PDC receiver channel requests.

When a half duplex peripheral is connected to the PDC, disabling the receiver channel requests also disables the transmitter channel requests.

### • TXTEN: Transmitter Transfer Enable

0 = No effect.

1 = Enables the PDC transmitter channel requests.

When a half duplex peripheral is connected to the PDC, it enables the transmitter channel requests only if RXTEN is not set. It is forbidden to set both TXTEN and RXTEN for a half duplex peripheral.

### • TXTDIS: Transmitter Transfer Disable

0 = No effect.

1 = Disables the PDC transmitter channel requests.

When a half duplex peripheral is connected to the PDC, disabling the transmitter channel requests disables the receiver channel requests.

## 24.4.10 Transfer Status Register

| Register Name: | PERIPH  | _PTSR |    |    |    |    |       |

|----------------|---------|-------|----|----|----|----|-------|

| Access Type:   | Read-on | lly   |    |    |    |    |       |

| 31             | 30      | 29    | 28 | 27 | 26 | 25 | 24    |

| -              | -       | _     | -  | -  | -  | -  | -     |

| 23             | 22      | 21    | 20 | 19 | 18 | 17 | 16    |

| -              | -       | —     | -  | -  | -  | -  | -     |

| 15             | 14      | 13    | 12 | 11 | 10 | 9  | 8     |

| -              | -       | _     | -  | -  | -  | -  | TXTEN |

| 7              | 6       | 5     | 4  | 3  | 2  | 1  | 0     |

| -              | _       | -     | _  | _  | _  | _  | RXTEN |

### • RXTEN: Receiver Transfer Enable

0 = PDC Receiver channel requests are disabled.

1 = PDC Receiver channel requests are enabled.

#### • TXTEN: Transmitter Transfer Enable

0 = PDC Transmitter channel requests are disabled.

1 = PDC Transmitter channel requests are enabled.