# STM32H7 Basic Timers

**VGRS 2023**

Pa3cio Bulić

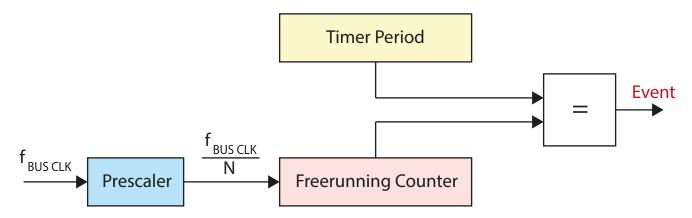

### Timers

- A timer is a circuit that enables the system to have the "knowledge of time" increments (or decrements) on the basis of a programmable clock source. A timer is essential for precise timing and control.

- A timer can generate interrupts

- The hardware of TIMER is composed by three basic memory-mapped registers:

- FREERUNNING COUNTER: increments by one for each clock cycle

- PRESCALER: The prescaler accumulates a prescribed number of bus clocks before issuing a clock tick to the timer.

- PERIOD: It represents the time it takes for the timer's counter to reach its maximum value and reset back to zero.

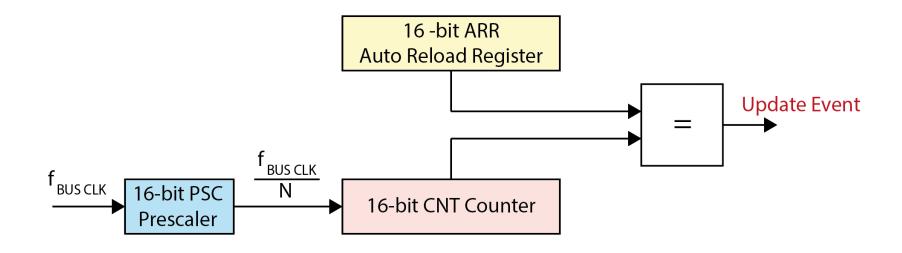

# Basic timers in STM32H750 (TIM6, TIM7)

STM32H7 contains two basic counter: TIM6 and TIM7.

$$f_{UpdateEvent} = \frac{f_{BusClock}}{(PSC+1)(ARR+1)}$$

$$T_{UpdateEvent} = T_{BusClock} \times (PSC+1) \times (ARR+1)$$

# Basic timers in STM32H750 (TIM6, TIM7)

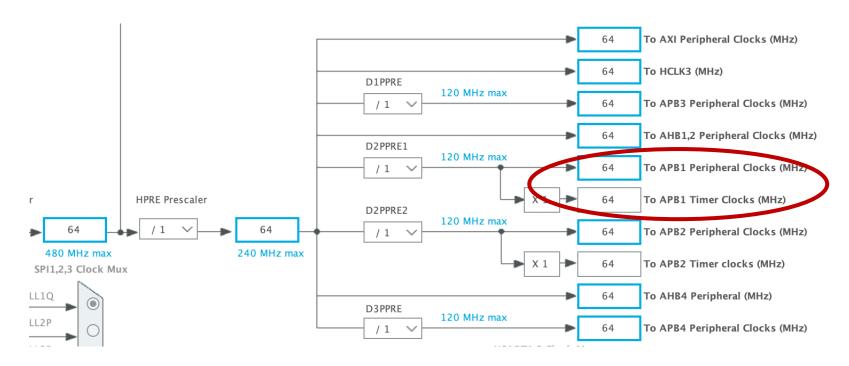

TIM6 and TIM7 are connected to APB1 bus.

# Timer auto-reload register

#### 42.4.8 TIMx auto-reload register (TIMx\_ARR)(x = 6 to 7)

Address offset: 0x2C

Reset value: 0xFFFF

| 15 | 14        | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    | ARR[15:0] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| rw | rw        | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 15:0 ARR[15:0]: Prescaler value

ARR is the value to be loaded into the actual auto-reload register.

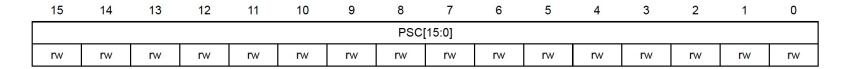

# Timer prescaler register

#### 42.4.7 TIMx prescaler $(TIMx_PSC)(x = 6 \text{ to } 7)$

Address offset: 0x28

Reset value: 0x0000

Bits 15:0 **PSC[15:0]**: Prescaler value

The counter clock frequency CK\_CNT is equal to  $f_{CK}$  PSC / (PSC[15:0] + 1).

PSC contains the value to be loaded into the active prescaler register at each update event. (including when the counter is cleared through UG bit of TIMx\_EGR register or through trigger controller when configured in "reset mode").

# Timer control register 1

#### 42.4.1 TIMx control register 1 (TIMx\_CR1)(x = 6 to 7)

Address offset: 0x00

Reset value: 0x0000

| 15   | 14   | 13   | 12   | 11           | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3   | 2   | 1    | 0   |

|------|------|------|------|--------------|------|------|------|------|------|------|------|-----|-----|------|-----|

| Res. | Res. | Res. | Res. | UIFRE<br>MAP | Res. | Res. | Res. | ARPE | Res. | Res. | Res. | ОРМ | URS | UDIS | CEN |

|      |      |      |      | rw           |      |      |      | rw   |      |      |      | rw  | rw  | rw   | rw  |

#### Bit 1 **UDIS**: Update disable

This bit is set and cleared by software to enable/disable UEV event generation.

0: UEV enabled. The Update (UEV) event is generated by one of the following events:

- Counter overflow/underflow

- Setting the UG bit

- Update generation through the slave mode controller

Buffered registers are then loaded with their preload values.

1: UEV disabled. The Update event is not generated, shadow registers keep their value (ARR, PSC). However the counter and the prescaler are reinitialized if the UG bit is set or if a hardware reset is received from the slave mode controller.

Bit 0 CEN: Counter enable

0: Counter disabled

1: Counter enabled

Note: Gated mode can work only if the CEN bit has been previously set by software. However trigger mode can set the CEN bit automatically by hardware.

CEN is cleared automatically in one-pulse mode, when an update event occurs.

Bit 7 **ARPE**: Auto-reload preload enable

0: TIMx ARR register is not buffered.

1: TIMx\_ARR register is buffered.

Bits 6:4 Reserved, must be kept at reset value.

Bit 3 **OPM**: One-pulse mode

0: Counter is not stopped at update event

1: Counter stops counting at the next update event (clearing the CEN bit).

# Timer DMA/Interrupt enable register

#### 42.4.3 TIMx DMA/Interrupt enable register (TIMx\_DIER)(x = 6 to 7)

Address offset: 0x0C

Reset value: 0x0000

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8   | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0   |

|------|------|------|------|------|------|------|-----|------|------|------|------|------|------|------|-----|

| Res. | UDE | Res. | UIE |

|      |      |      |      |      |      |      | rw  |      |      |      |      |      |      |      | rw  |

Bits 15:9 Reserved, must be kept at reset value.

Bit 8 **UDE**: Update DMA request enable

0: Update DMA request disabled.

1: Update DMA request enabled.

Bits 7:1 Reserved, must be kept at reset value.

Bit 0 **UIE**: Update interrupt enable

0: Update interrupt disabled.

1: Update interrupt enabled.

# Timer status register

#### 42.4.4 TIMx status register $(TIMx_SR)(x = 6 \text{ to } 7)$

Address offset: 0x10

Reset value: 0x0000

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0     |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|

| Res. | UIF   |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | rc_w0 |

Bits 15:1 Reserved, must be kept at reset value.

Bit 0 **UIF**: Update interrupt flag

This bit is set by hardware on an update event. It is cleared by software.

- 0: No update occurred.

- 1: Update interrupt pending. This bit is set by hardware when the registers are updated:

- At overflow or underflow regarding the repetition counter value and if UDIS = 0 in the TIMx CR1 register.

- When CNT is reinitialized by software using the UG bit in the TIMx\_EGR register, if URS = 0 and UDIS = 0 in the TIMx\_CR1 register.

# Prescaler operation

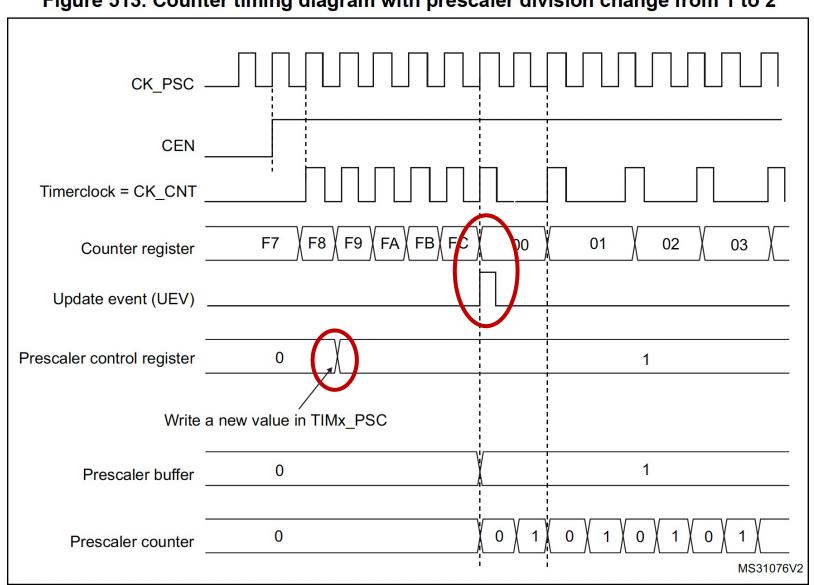

Figure 513. Counter timing diagram with prescaler division change from 1 to 2

Prescaler operation

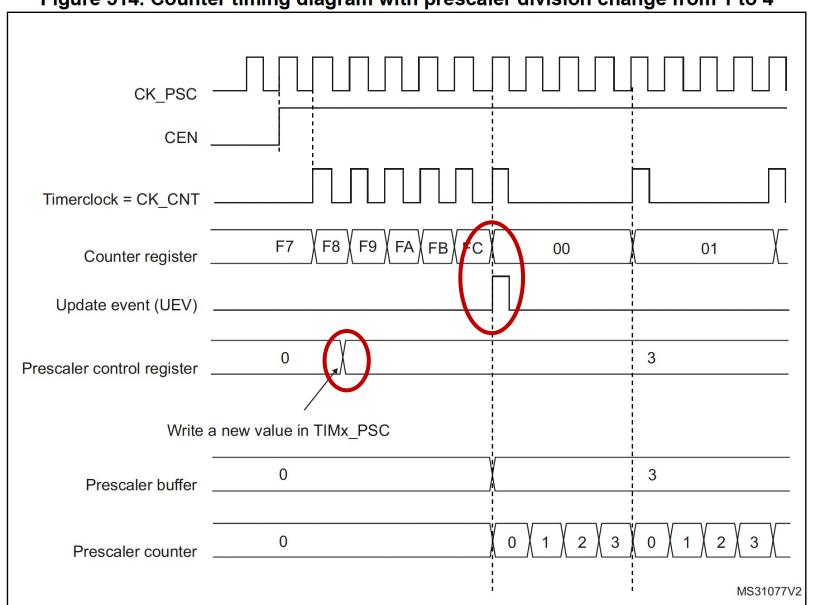

Figure 514. Counter timing diagram with prescaler division change from 1 to 4

## Timer operation

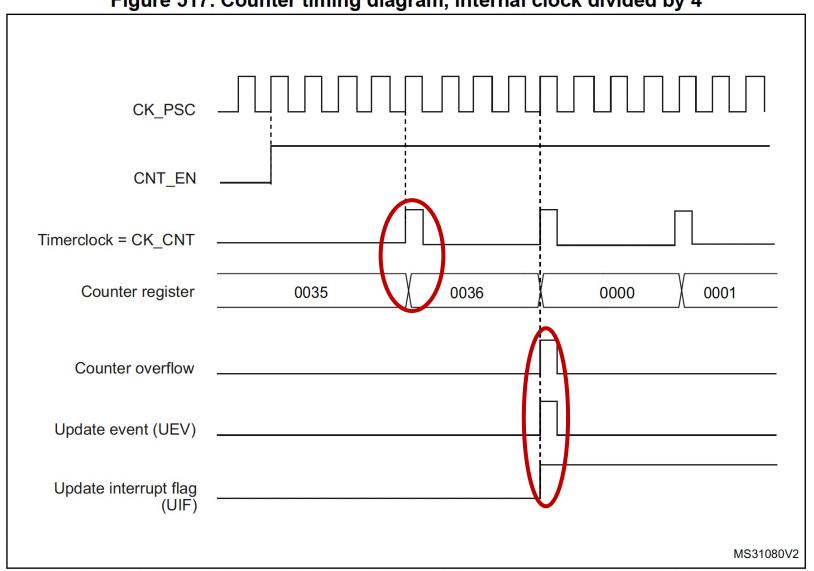

Figure 517. Counter timing diagram, internal clock divided by 4

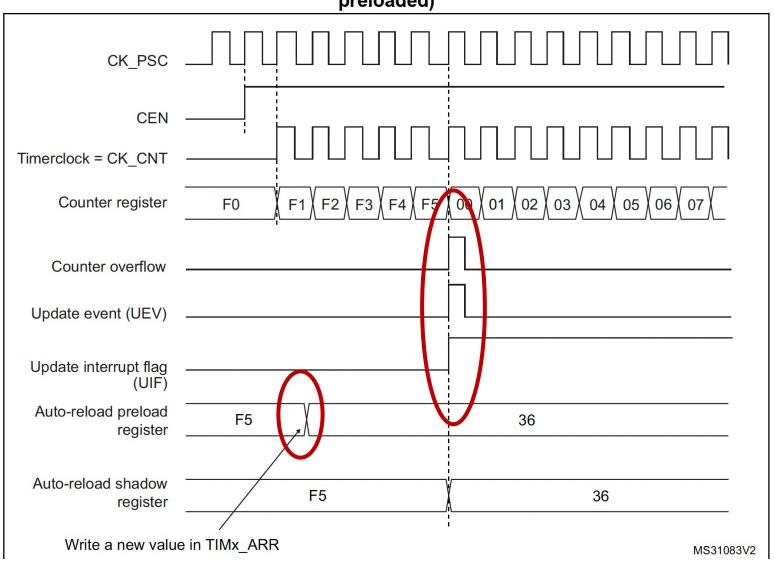

# Timer operation – ARR preloading (buffering)

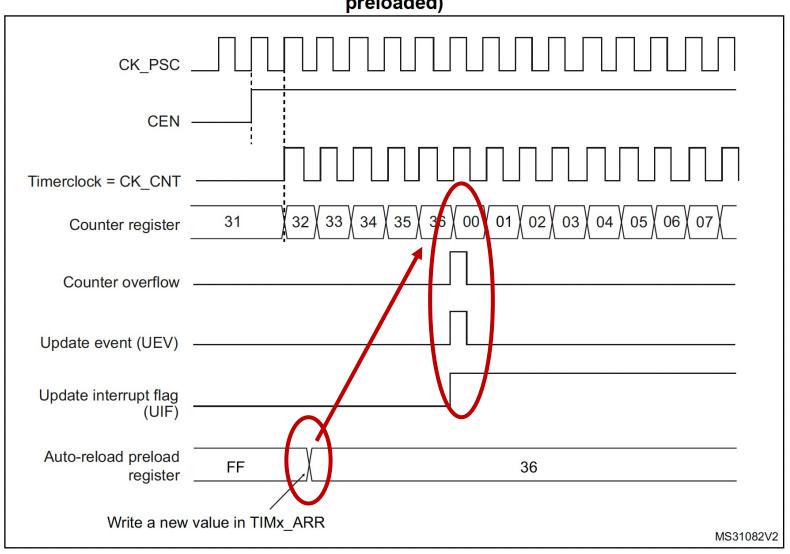

- The auto-reload register (ARR) holds the value at which the counter is automatically reloaded, creating a periodic timer behavior. When the counter reaches the value stored in the auto-reload register, it resets to zero, and the process repeats.

- The ARR preloading feature (buffering) allows you to load a new value into the auto-reload register without affecting the ongoing count. Instead of immediately taking the new value, it is only applied when an update event occurs.

- Timer ARR register preloading (buffering) provides several advantages:

- The new value is loaded atomically, preventing glitches or inconsistencies in the timer operation.

- Preloading allows synchronization of updates with specific timer events, ensuring precise control

over the timer's behavior.

- By updating the registers at a specific moment, preloading can help reduce timing jitter in applications where precise timing is crucial.

# Timer operation – ARR not preloaded

Figure 519. Counter timing diagram, update event when ARPE = 0 (TIMx\_ARR not preloaded)

# Timer operation – ARR preloaded

Figure 520. Counter timing diagram, update event when ARPE=1 (TIMx\_ARR preloaded)

## Timer registers abstraction

```

def struct

IO uint32 t CR1;

__IO uint32_t CR2;

IO uint32 t SMCR;

IO uint32 t DIER;

__IO uint32_t SR;

IO uint32 t EGR;

IO uint32 t CCMR1;

___IO uint32_t CCMR2;

__IO uint32_t CCER;

__IO uint32_t CNT;

IO uint32 t PSC;

IO uint32 t ARR;

__IO uint32_t RCR;

IO uint32 t CCR1;

__IO uint32_t CCR2;

_IO uint32_t CCR3;

IO uint32 t CCR4;

__IO uint32_t BDTR;

IO uint32 t DCR;

IO uint32 t DMAR;

uint32 t

RESERVED1;

IO uint32 t CCMR3;

__IO uint32_t CCR5;

I0 uint32 t CCR6;

IO uint32 t AF1;

__IO uint32_t AF2;

IO uint32 t TISEL;

} TIM_TypeDef;

```

```

#define TIM2

#define TIM3

#define TIM4

#define TIM5

#define TIM6

#define TIM7

```

```

((TIM_TypeDef *) 0x4000000UL)

((TIM_TypeDef *) 0x40000400UL)

((TIM_TypeDef *) 0x40000800UL)

((TIM_TypeDef *) 0x40000C00UL)

((TIM_TypeDef *) 0x40001400UL)

((TIM_TypeDef *) 0x40001400UL)

```

## Timer initalization structure

```

typedef struct

/*!< Specifies the prescaler value used to divide the TIM clock.

uint32 t Prescaler;

This parameter can be a number between Min Data = 0 \times 0000 and Max Data = 0 \times FFFF * /

uint32 t CounterMode;

This parameter can be a value of @ref TIM Counter Mode */

uint32 t Period;

uint32 t AutoReloadPreload;

/*!< Specifies the auto-reload preload.

This parameter can be a value of @ref TIM_AutoReloadPreload */

TIM Base InitTypeDef;

```

$$f_{UpdateEvent} = \frac{f_{BusClock}}{(Prescaler + 1)(Period + 1)}$$

$$T_{UpdateEvent} = T_{BusClock} \times (Prescaler + 1) \times (Period + 1)$$

## Timer handle structure

### Timer initialization and start

```

TIM_HandleTypeDef htim7;

htim7.Instance = TIM7;

htim7.Init.Prescaler = 1;

htim7.Init.CounterMode = TIM_COUNTERMODE_UP;

htim7.Init.Period = 65535;

htim7.Init.AutoReloadPreload = TIM_AUTORELOAD_PRELOAD_ENABLE;

if (HAL_TIM_Base_Init(&htim7) != HAL_OK)

{

Error_Handler();

}

```

Start timer without interrupts on update events:

Start timer with interrupts on update events:

```

HAL_TIM_Base_Start(&htim7);

```

```

HAL_TIM_Base_Start_IT(&htim7);

```

### Timer initialization:

```

void TIM_Base_SetConfig(TIM_TypeDef *TIMx, const TIM_Base_InitTypeDef *Structure)

uint32_t tmpcr1;

tmpcr1 = TIMx->CR1;

/* Set TIM Time Base Unit parameters -

if (IS TIM COUNTER MODE SELECT INSTANCE(TIMx))

/* Select the Counter Mode */

tmpcr1 &= ~(TIM_CR1_DIR | TIM_CR1_CMS);

tmpcr1 |= Structure->CounterMode;

if (IS TIM CLOCK DIVISION INSTANCE(TIMx))

/* Set the clock division */

tmpcr1 &= ~TIM CR1 CKD;

tmpcr1 |= (uint32_t)Structure->ClockDivision;

/* Set the auto-reload preload */

MODIFY_REG(tmpcr1, TIM_CR1_ARPE, Structure->AutoReloadPreload);

TIMx->CR1 = tmpcr1;

/* Set the Autoreload value */

TIMx->ARR = (uint32 t)Structure->Period;

/* Set the Prescaler value */

TIMx->PSC = Structure->Prescaler;

```

```

HAL_StatusTypeDef HAL_TIM_Base_Init(TIM_HandleTypeDef *htim)

/* Check the TIM handle allocation */

if (htim == NULL)

return HAL_ERROR;

eck the parameters */

t param(IS TIM INSTANCE(htim->Instance));

t param(IS TIM COUNTER MODE(htim->Init.CounterMode));

t_param(IS_TIM_CLOCKDIVISION_DIV(htim->Init.ClockDivision));

t param(IS TIM PERIOD(htim, htim->Init.Period));

t param(IS TIM AUTORELOAD PRELOAD(htim->Init.AutoReloadPreload));

if (htim->State == HAL_TIM_STATE_RESET)

/* Allocate lock resource and initialize it */

htim->Lock = HAL UNLOCKED;

#1f (USE_HAL_TIM_REGISTER_CALLBACKS == 1)

/* reset interrupt callbacks to legacy **eak callbacks */

TIM Resettallback(htim);

if (htim->Base_MspInit a lback == NULL)

htim->Base rispInitCallback = HAL TIM Base MspInit;

\primest Init the low level hardware : GPIO, CLOCK, NvIC st/

htim->Base MspInitCallback(htim);

#else

/* Init the low level nardware : GPIU, CLUCK, NVIC */

HAL TIM Base MspInit(htim);

#endif /* USE_HAL_TIM_REGISTER_CALLBACKS */

/* Set the TIM state */

htim->State = HAL_TIM_STATE_BUSY;

/本 JEL LINE ITHE DOZE CONTINUATION 本/

TIM_Base_SetConfig(htim->Instance, &htim->Init);

```

### Timer initialization:

Implement your own Msp\_Init function which:

- enables timer clock

- sets NVIC (priority+enable)

```

void HAL_TIM_Base_MspInit(TIM_HandleTypeDef* htim_base)

if(htim_base->Instance==TIM7)

_HAL_RCC_TIM7_CLK_ENABLE();

/* TIM7 interrupt Init */

HAL_NVIC_SetPriority(TIM7_IRQn, 5, 0);

HAL_NVIC_EnableIRQ(TIM7_IRQn);

```

### Timer initialization:

Implement your own Msp\_Init function which:

- enables timer clock

- sets NVIC (priority+enable)

```

void HAL_TIM_Base_MspInit(TIM_HandleTypeDef* htim_base)

if(htim_base->Instance==TIM7)

_HAL_RCC_TIM7_CLK_ENABLE();

/* TIM7 interrupt Init */

HAL_NVIC_SetPriority(TIM7_IRQn, 5, 0);

HAL_NVIC_EnableIRQ(TIM7_IRQn);

```

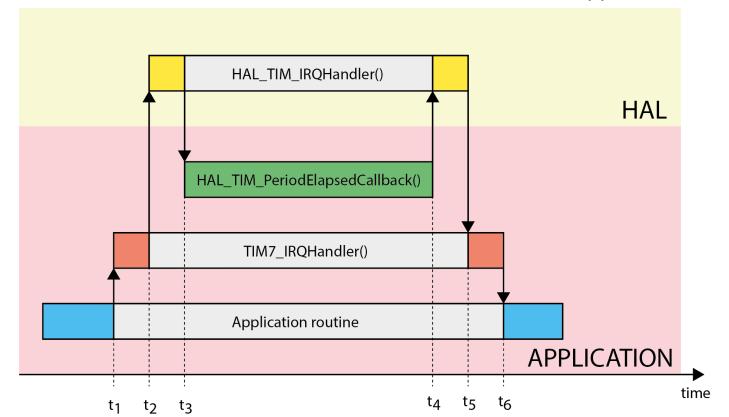

## Timer interrupt processing in HAL:

- STM32 HAL library follows a callback-oriented programming model and uses callback functions:

- This approach decouples the handling of hardware events from the core library, allowing users to define their own behaviors in response to interrupts.

- It provides a flexible and modular approach to handle interrupts, making the HAL library adaptable to different

application requirements.

- Users have the freedom to define specific actions in response to interrupts, ensuring that the HAL remains

versatile and customizable across diverse embedded applications.

This mechanism is used by almost all IRQ handler routines inside the HAL.

## Timer interrupt processing in HAL:

```

void TIM7_IRQHandler(void)

{

HAL_TIM_IRQHandler(&htim7);

}

```

```

if (htim->Instance == TIM7) {

HAL_GPIO_TogglePin(GPIOD, GPIO_PIN_3);

}

```

```

/* TIM Update event */

if (__HAL_TIM_GET_FLAG(htim, TIM_FLAG_UPDATE) != RESET)

{

if (__HAL_TIM_GET_IT_SOURCE(htim, TIM_IT_UPDATE) != RESET)

{

__HAL_TIM_CLEAR_IT(htim, TIM_IT_UPDATE);

#if (USE_HAL_TIM_REGISTER_CALLBACKS == 1)

htim->PeriodElapsedCallback(htim);

#else

HAL_TIM_PeriodElapsedCallback(htim);

#else

HAL_TIM_PeriodElapsedCallback(htim);

#endif /: USE_HAL_TIM_REGISTER_CALLBACKS ::/

```